# Letter of Intent for the Phase-II Upgrade of the ATLAS Experiment

#### **ATLAS Collaboration**

#### ABSTRACT:

This Letter of Intent presents a plan for preserving and improving the current detection capabilities of the ATLAS detector to meet the challenges and take advantage of operating at the High Luminosity LHC (HL-LHC). From 2024, the HL-LHC will provide unprecedented pp luminosities to ATLAS, resulting in an additional integrated luminosity of around 2500 fb<sup>-1</sup> over ten years. This will present a unique opportunity to substantially extend the mass reach in searches for many signatures of new physics, in several cases well into the multi-TeV region, and to significantly extend the study of the properties of the Higgs boson.

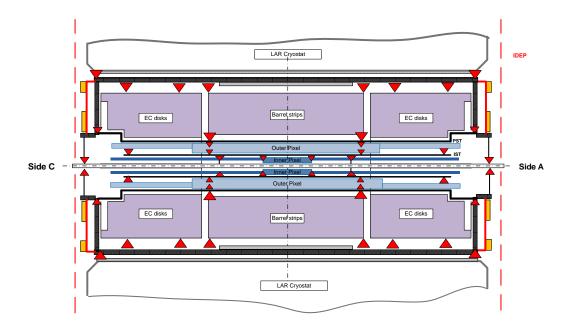

The increased luminosity and the accumulated radiation damage will render the current Inner Tracker no longer suitable for long term operations. It will need to be replaced with a new all-silicon tracker to maintain tracking performance in the high occupancy environment and to cope with the increase of approximately a factor of ten in the total radiation fluence. New technologies are used to ensure that the system can survive this harsh radiation environment and to optimise the material distribution, while the new readout scheme allows the implementation of a track trigger contributing to the improvements in the ATLAS triggering capabilities.

The very high luminosities also present significant challenges to the operation and performance of the rest of the detector systems as well as the trigger; the consequent high number of collisions per crossing will degrade the performance of ATLAS unless the LAr and Tile calorimeters and the Muon Spectrometer readout systems are upgraded. A new trigger architecture will be implemented exploiting the upgrades of the detector readout systems that will maintain and improve the event selection.

The increased luminosity may also degrade the performance of the forward calorimetry. Options for upgrading the hadronic endcap calorimeter readout electronics and the forward calorimeter detector design are being investigated to address the performance degradation, if this proves to be required.

Finally, the computing and software must be upgraded to meet the challenges of the increased luminosity and changes in computer architectures.

KEYWORDS: ATLAS, LHC, HL-LHC, Upgrade, CERN.

# Contents

| 1. | Exe                                                      | cutive Summary                                                         | 3   |  |

|----|----------------------------------------------------------|------------------------------------------------------------------------|-----|--|

| 2. | Upg                                                      | rade of the Trigger and Data-Flow Systems                              | 6   |  |

|    | 2.1                                                      | Projected trigger rates for the Phase-I trigger at HL-LHC luminosities | 7   |  |

|    | 2.2                                                      | The Phase-II Trigger Architecture                                      | 9   |  |

|    | 2.3                                                      | Calorimeter Trigger                                                    | 11  |  |

|    | 2.4                                                      | Muon Trigger                                                           | 13  |  |

|    | 2.5                                                      | Level-1 Track Trigger                                                  | 15  |  |

|    | 2.6                                                      | Central Trigger System                                                 | 19  |  |

|    | 2.7                                                      | Data Acquistion                                                        | 21  |  |

|    | 2.8                                                      | High-Level Trigger                                                     | 25  |  |

| 3. | Upgrade of the Liquid-Argon Calorimeter                  |                                                                        |     |  |

|    | 3.1                                                      | Liquid-Argon Readout Electronics                                       | 27  |  |

|    | 3.2                                                      | Liquid-Argon Calorimeter Detectors and HEC Cold Electronics            | 32  |  |

| 4. | Upgrade of the Tile Calorimeter                          |                                                                        |     |  |

|    | 4.1                                                      | Upgrade of the TileCal readout                                         | 41  |  |

|    | 4.2                                                      | The TileCal Demonstrator                                               | 44  |  |

| 5. | Upgrade of the Muon System                               |                                                                        |     |  |

|    | 5.1                                                      | Upgrade of the MDT tracking system                                     | 48  |  |

|    | 5.2                                                      | Upgrade of the RPC Muon Barrel trigger                                 | 49  |  |

|    | 5.3                                                      | Upgrade of the Muon End-cap trigger (TGC chambers)                     | 52  |  |

|    | 5.4                                                      | Use of MDT precision coordinates to sharpen the high- $p_T$ threshold  | 53  |  |

| 6. | Upgrade of the Inner Tracking System                     |                                                                        |     |  |

|    | 6.1                                                      | Motivation and requirements                                            | 57  |  |

|    | 6.2                                                      | Phase-II tracker layout and performance                                | 61  |  |

|    | 6.3                                                      | The pixel system                                                       | 69  |  |

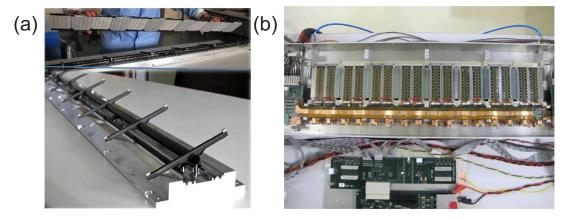

|    | 6.4                                                      | The strip system                                                       | 84  |  |

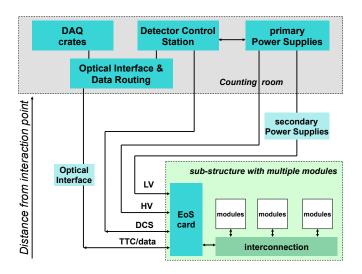

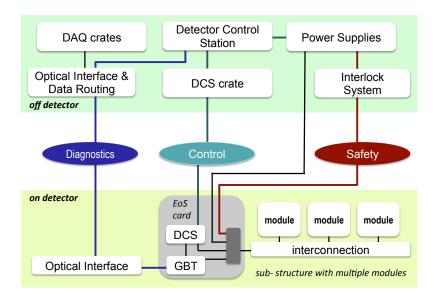

|    | 6.5                                                      | Common readout, data acquisition and controls for pixels and strips    | 97  |  |

|    | 6.6                                                      | System engineering                                                     | 99  |  |

| 7. | Upgrades of computing and Software for high luminosities |                                                                        |     |  |

|    | 7.1                                                      | Computing Model Considerations                                         | 106 |  |

|    | 7.2                                                      | Frameworks                                                             | 107 |  |

|    | 7.3                                                      | I/O, persistence, and increasingly many-core architectures             | 108 |  |

|    | 7.4                                                      | Simulation                                                             | 109 |  |

|    | 7.5                                                      | Reconstruction                                                         | 110 |  |

| 11. | Cone                           | clusions                                    | 136 |

|-----|--------------------------------|---------------------------------------------|-----|

| 10. | Reso                           | ources                                      | 134 |

|     | 9.4                            | Radioprotection requirements                | 131 |

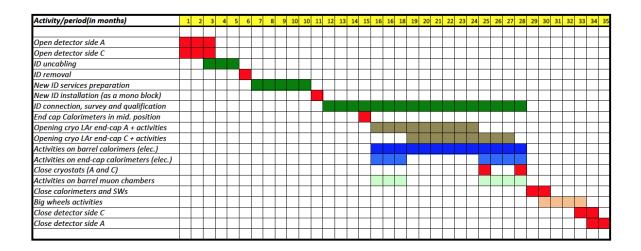

|     | 9.3                            | LAr end-cap activities, additional scenario | 130 |

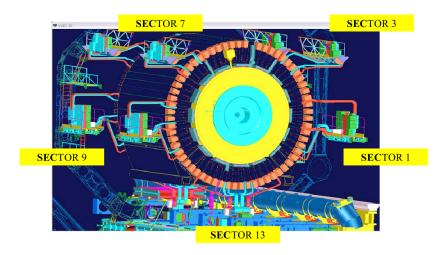

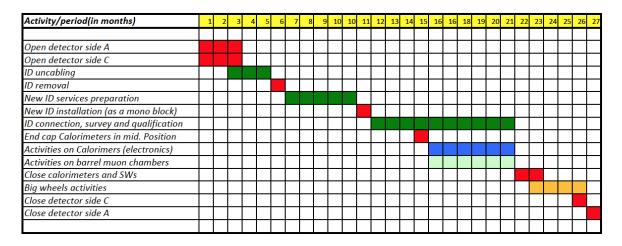

|     | 9.2                            | Operation layouts and configurations        | 130 |

|     | 9.1                            | Requirements                                | 129 |

| 9.  | Installation and commissioning |                                             | 129 |

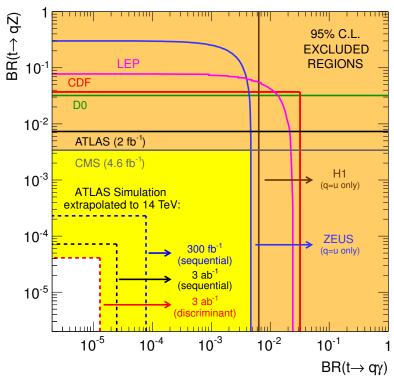

|     | 8.6                            | FCNC in top decays                          | 127 |

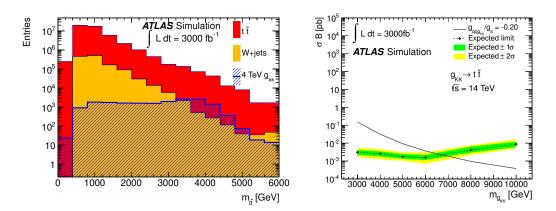

|     | 8.5                            | Exotics                                     | 124 |

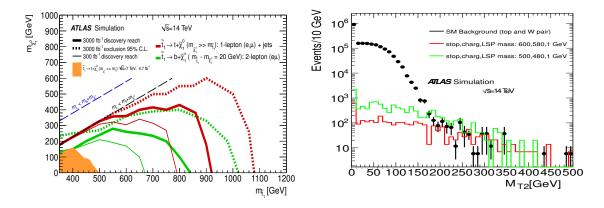

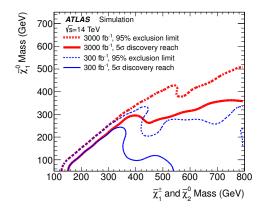

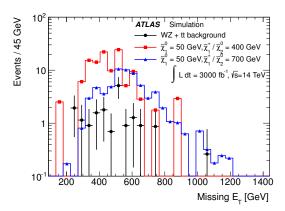

|     | 8.4                            | Supersymmetry searches and measurements     | 122 |

|     | 8.3                            | Weak boson scattering                       | 120 |

|     | 8.2                            | Measurements of the Higgs-like boson        | 115 |

|     | 8.1                            | Introduction                                | 114 |

| 8.  | Physics Goals                  |                                             | 114 |

|     | 7.10                           | Data Preservation                           | 113 |

|     | 7.9                            | Analysis                                    | 112 |

|     | 7.8                            | Distributed Computing                       | 112 |

|     | 7.7                            | Software Infrastructure                     | 111 |

|     | 7.6                            | Databases and Database technologies         | 111 |

# 1. Executive Summary

The High Luminosity LHC (HL-LHC) will begin collisions around 2024 and will provide a levelled instantaneous luminosity of  $5\times10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> with the aim of delivering an additional 2500 fb<sup>-1</sup> to ATLAS over ten years [1]. The HL-LHC will remain the proton-proton discovery machine at the high energy frontier, and provide a large dataset for precision measurements. The upgrades of the LHC will first see an intermediate stage: Phase-I, when the peak instantaneous luminosity will increase to  $2.2\times10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> (around twice the nominal) and delivering around 300-400 fb<sup>-1</sup> integrated luminosity by 2022. The proposed ATLAS Upgrade programme for Phase-I operation is described in [2].

This Letter of Intent describes the proposed Phase-II upgrades of the ATLAS detector that will allow operation at five times the nominal LHC luminosity,  $5 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>, and the full exploitation of the physics accessible with a total integrated luminosity of up to 3000 fb<sup>-1</sup>, with approximately 2500 fb<sup>-1</sup> collected at the HL-LHC.

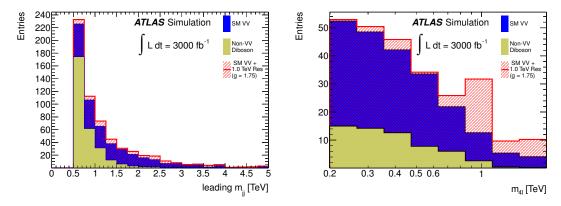

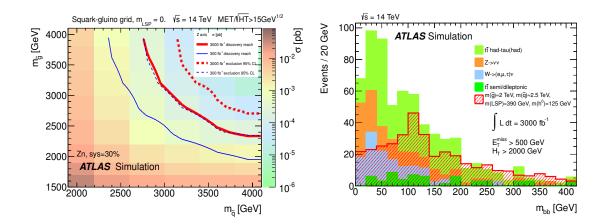

The large luminosity extends the energy scales that can be studied in high energy boson-boson scattering, to study the EWSB mechanism, and to probe for signatures of new physics predicted by models such as SUSY and extra dimensions well into the multi-TeV region. The range of new physics signatures includes: searches for high mass gauge bosons (requiring good lepton momentum resolution up to high transverse momenta); reconstruction of complex SUSY cascade decays (requiring triggering and reconstruction of low  $p_T$  leptons and identification of heavy flavours); and searches for resonances in  $t\bar{t}$ -pairs (requiring reconstruction of leptons and heavy flavours in highly boosted topologies).

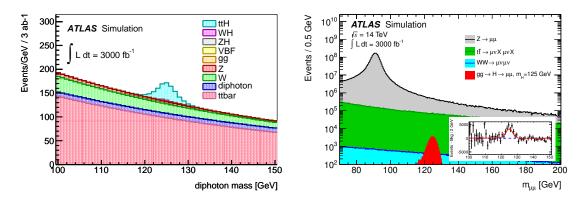

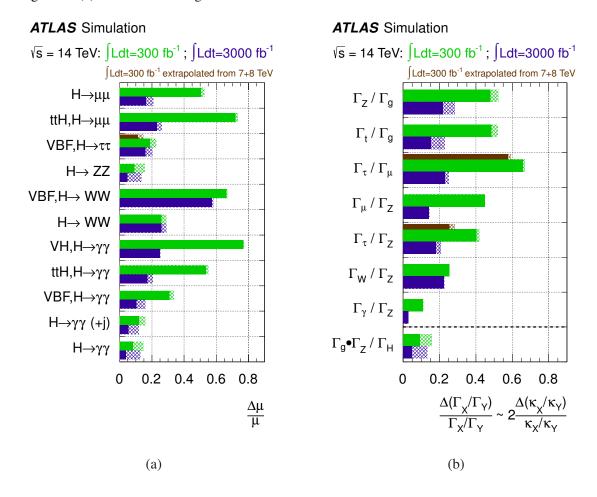

The large data sample will allow significant improvements in the precision of the measurements of the Higgs couplings, achieving precisions in a range between 5% and 30%. This will also allow rare channels to be measured:  $H \to \mu\mu$ , vector boson fusion production of  $H \to \gamma\gamma$  and  $H \to \tau\tau$ , and associated production with a top-pair:  $t\bar{t}H$  with  $H \to \gamma\gamma$ . These additional channels increase the precision with which the fermion couplings can be measured and improve the limits on new physics that can be set from loops in, for example,  $gg \to H$  and  $H \to \gamma\gamma$ . The full luminosity will also allow the Higgs self-coupling to be studied for the first time in channels such as  $HH \to \tau\tau bb$  and  $HH \to \gamma\gamma bb$  channels.

The increased instantaneous luminosity at the HL-LHC results in the expected mean number of interactions per bunch crossing increasing from  $\sim 55$  at  $2\times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> to  $\sim 140$  at  $5\times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> (assuming a bunch crossing time of 25 ns) and the consequent increase in the integrated luminosity requires a detector able to operate after exposure to large particle fluences. These impact the experiment through increased detector occupancy and radiation damage. To allow for some safety margin, the design studies for the proposed upgrades assume a maximum instantaneous luminosity of  $7\times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>, 200 pile-up events, and an integrated luminosity of 3000 fb<sup>-1</sup> over ten years where appropriate.

At the end of the current LHC programme the ATLAS detector will be running with components that are 15-20 years old. After the intermediate Phase-I upgrade, the silicon tracking systems will be approaching the end of their lifetimes: 700 fb<sup>-1</sup> for the strip system and 400 fb<sup>-1</sup> for the pixel system. Moreover, the higher luminosity will increase significantly the occupancies in both the silicon detectors, and the occupancy in the straw tube transition radiation tracker (TRT) will

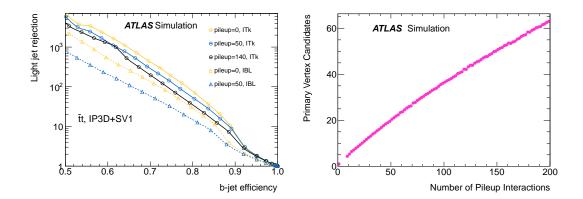

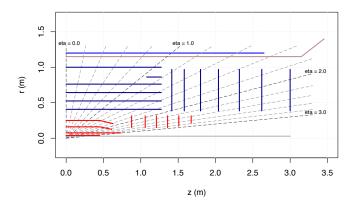

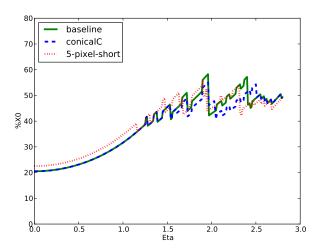

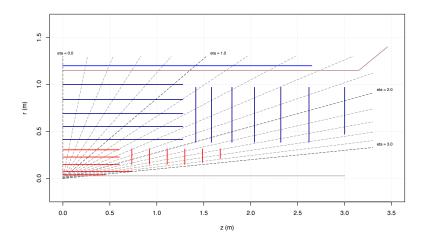

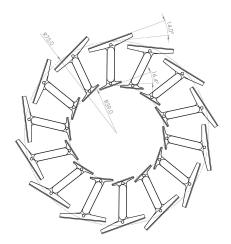

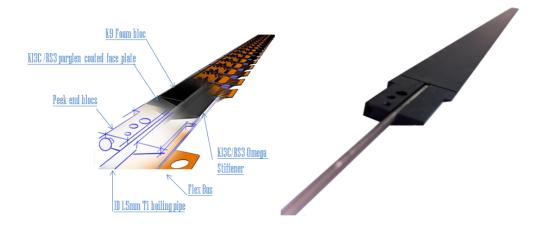

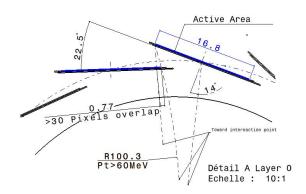

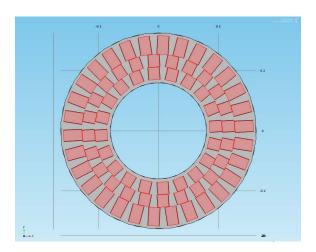

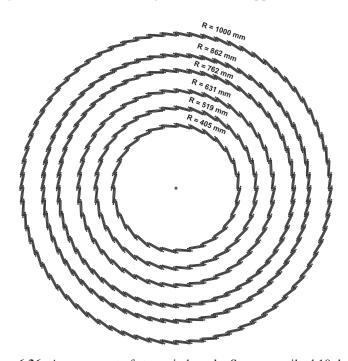

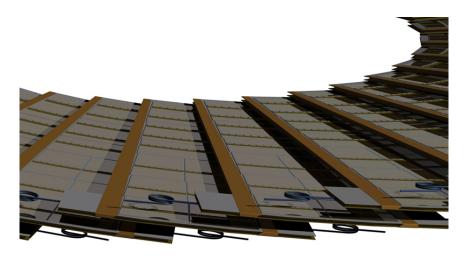

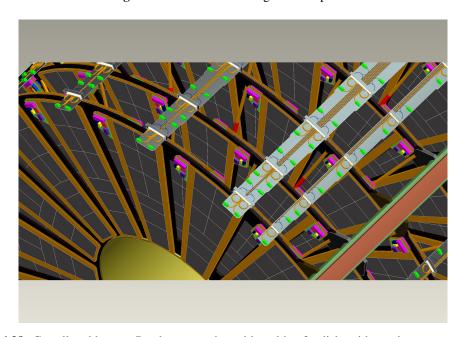

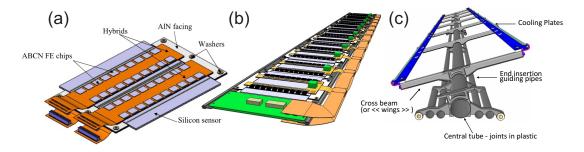

reach  $\sim 100\%$  at  $5\times10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>, severely compromising the tracking performance. Therefore the need for good performance in vertex and track reconstruction, lepton identification and heavy flavour tagging, even in the high occupancy and radiation fluence environment of the HL-LHC, require a complete replacement of the current tracking system. Based on the experience gained with the current tracker, a new all-silicon tracker design has been developed. The new layout consists of pixel layers to provide pattern recognition and precision position measurements close to the vertex and which are complemented by a strip system that provides accurate tracking at larger radii. Simulations of the performance of the new layout show that the basic parameters of the tracking performance (impact parameters in  $r\phi$  and z, and momentum resolution) can be preserved and even improved in processes with 200 pile-up events, and that the physics performance, such as the b-tagging performance and the mass resolution, is maintained in this high pile-up environment. The system design has been optimised to minimise the material by using modern light carbon fibrebased engineering materials as support structures, and by a careful design of the services and of their routing. Developments of silicon sensor technologies have been shown to provide the required radiation hardness, complemented by the use of modern ASIC technologies to develop front-end electronics with the necessary radiation tolerance. The readout of the tracker must be upgraded to provide the increased bandwidth required to cope with the higher occupancies, and to accommodate the proposed TDAQ architecture and provide input for the new Level-1 track trigger.

With the large variety of opportunities for discoveries and precision measurements, it is essential that ATLAS maintains or improves its performance in triggering and precisely reconstructing the full range of physics objects (e,  $\mu$ ,  $\tau$ ,  $\gamma$ , jets, heavy flavour jets,  $E_T^{miss}$ ) over as large an acceptance as possible at the HL-LHC luminosity. Considering the recent discovery of a relatively low mass Higgs-like particle, it is envisaged, for example, to maintain  $p_T$ -thresholds at around 20 GeV for single lepton triggers, to preserve the acceptance of key signatures such as W and Z bosons and  $t\bar{t}$ - pairs. Extrapolating Phase-I trigger rates to HL-LHC luminosity, while maintaining low single-lepton thresholds, would require a total Level-1 rate of at least 500 kHz, which exceeds the trigger rate of 100 kHz that can be supported by the ATLAS detector in Phase I. Several architectures were considered to address this issue; the proposed baseline architecture uses a two-step first level hardware trigger, in which the first step, based on the Phase-I Level-1 trigger architecture and hardware, provides a Level-0 accept at a rate of at least 500 kHz within a latency of 6  $\mu$ s. In the second step, a new Level-1 system reduces the rate to 200 kHz, primarily using tracking information, within an additional latency of 14  $\mu$ s. Studies have shown that the required reduction factor can be achieved with the proposed track trigger.

The current readout electronics of the detector systems, which operates at a maximum rate of 100 kHz with a maximum latency of up to 3  $\mu$ s, is not compatible with the baseline trigger architecture described above. This mandates the replacement of the detector readout electronics to accommodate the new two-step Level-0/Level-1 architecture: the higher trigger accept rates and the extended latencies at both Level-0 and Level-1. The replacement of the calorimeter and muon readout electronics can also be used to provide the full calorimeter granularity at Level-1 and an improved muon  $p_T$  resolution at Level-0 or Level-1 using the monitored drift tube (MDT) information. As already mentioned, the present tracker readout does not have sufficient bandwidth to cope with the HL-LHC luminosity and will be replaced as part of the tracker upgrade, including the implementation of a Level-0/Level-1 architecture for a Region-of-Interest based track trigger.

The combination of a Level-1 track trigger and the additional information from the calorimeter and muons will lead to a robust trigger system capable of adapting to the HL-LHC luminosity, ensuring that ATLAS will be able to fully exploit the physics potential of the increased luminosity.

The large particle fluxes may compromise the performance of the hadronic endcap calorimeter (HEC), due to lifetime issues in the cold electronics, and of the forward calorimeter (FCAL), reducing the acceptance. Confirmation of these issues and the course of actions that need to be taken is under investigation.

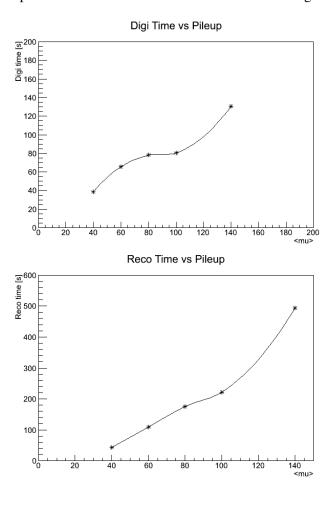

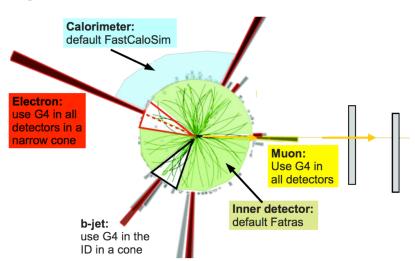

The computing and software of the experiment must evolve to meet the needs of the upgraded detector systems and to be able to handle the large event samples, and to adapt to new computing hardware architectures such as multi-core processors. The large event samples will require a new approach to simulation; mixing fast simulation, based on detector parameterisations, with full simulation at the event level, to optimise speed and event size. A new software framework will be developed that will be used both offline and for the high level trigger (HLT).

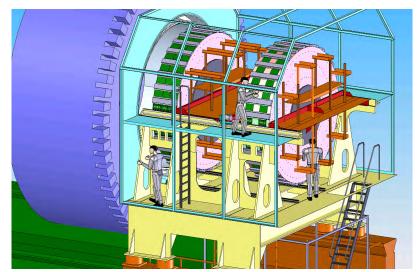

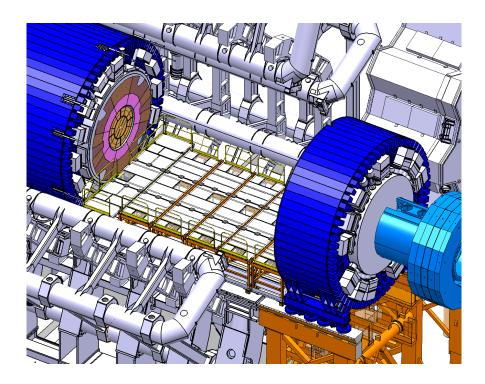

The proposed upgrades to the detector systems represent major changes and require careful implementation that allows for installation of the new tracker and access to the front- end electronics of the calorimeter and muon systems. Plans allowing for the possibility of opening the HEC cryostat to allow replacement of the front-end electronics and to install the new FCAL are under evaluation as they imply a longer shutdown period, and require additional radiation precautions and provision of clean environments, which must be weighed against the possible improvements in physics performance. Radioprotection is a major issue that will have to be faced during the Phase-II installation; work is underway to understand the radiation levels expected during installation and develop safe working practices.

The studies of HL-LHC physics channels are presented in chapter 8, after describing the performance of the upgraded detector. The proposed upgrades to the trigger and data acquisition are described first in chapter 2, since these influence all the other upgrades. The proposed upgrades of the readout electronics for the calorimeter systems are then described in chapters 3 and 4; and those for the muon system and the tracker in chapters 5 and 6. The performance, layout and technical description of the proposed new tracker are also detailed in chapter 6. Studies of the HEC cold electronics possible limitations and studies of the FCAL performance at high luminosity, along with possible upgrades, are discussed in chapter 3. The development of computing and software is discussed in chapter 7. The installation plan and schedule are described in chapter 9, including evaluation of the impact of replacing the HEC electronics and the FCAL. Finally the estimated CORE costs are presented in chapter 10.

# 2. Upgrade of the Trigger and Data-Flow Systems

The luminosities that will be delivered by the HL-LHC will provide a significant challenge to the ATLAS trigger and DAQ system, both in terms of the rates and increased data volume. This section describes the current plans for the modifications of the trigger and data acquisition systems.

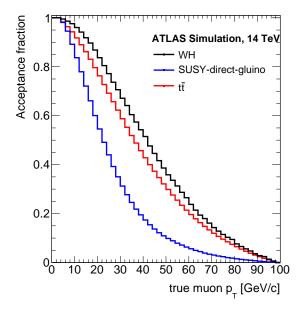

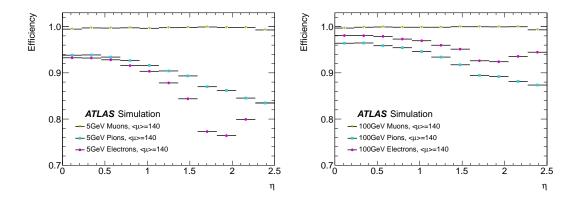

The requirements for the Phase-II trigger are closely tied to the ATLAS physics goals at the HL-LHC. Much of the upgrade of the Phase-II trigger is driven by the desire to maintain efficient triggers for isolated electrons and muons with thresholds around 20 GeV at luminosities of up to  $7 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. This goal is determined by the need to maintain good efficiency for the leptons produced in the decays of the electroweak bosons. The acceptance for muons from  $t\bar{t}$ , WH and SUSY processes as a function of the true muon  $p_T$  is shown in Figure 2.1, where an increase in threshold from 20 GeV to 30 GeV results in a reduction in acceptance of between  $\sim 1.3-1.8$ . There is also a clear physics need to maintain reasonable thresholds for tau leptons and photons. Finally, the trigger needs to be sufficiently flexible to be able to adapt to any new physics discoveries and changes in background conditions.

**Figure 2.1:** Acceptance of muons from  $t\bar{t}$ , WH and SUSY processes as a function of true muon momentum.

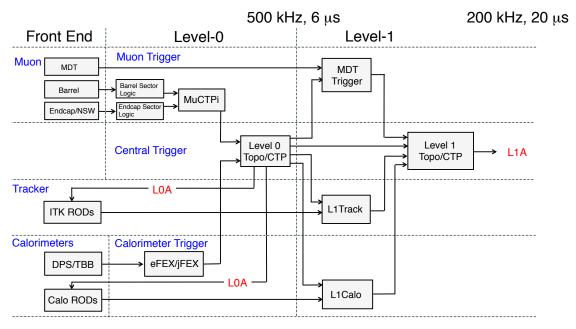

A new trigger architecture is being developed that is compatible with the constraints imposed by the detector and provides a flexible trigger with the potential to deliver the required performance. The main features are summarised below and details described in the following sections. As currently envisaged, the baseline design for the **Phase-II Trigger** is:

- a split Level-0/Level-1 hardware trigger with a total level-1 accept rate of 200 kHz and total latency of 20  $\mu$ s.

- the Level-0 trigger would distribute the Level-0 accept at a rate of at least 500 kHz within a latency of 6  $\mu$ s. The Phase-II Level-0 trigger is functionally the same as the Phase-I Level-1

system and consists of a feature extractor (FEX) based on calorimeter electromagnetic and jet triggers, and the Phase-I Level-1 muon trigger. The Level-0 accept is generated by the central trigger system which incorporates topological triggering capability.

- the Level-1 system will reduce the rate to  $200 \, \text{kHz}$  within an additional latency of  $14 \, \mu \text{s}$ . This reduction will be accomplished by the introduction of track information within a Region-of-Interest (RoI), full calorimeter granularity within the same RoI and the introduction of a refined muon selection based on the use of the MDT information.

- an increased use of offline-like algorithms in the High-Level Trigger (software trigger) with an anticipated readout rate of 5–10 kHz.

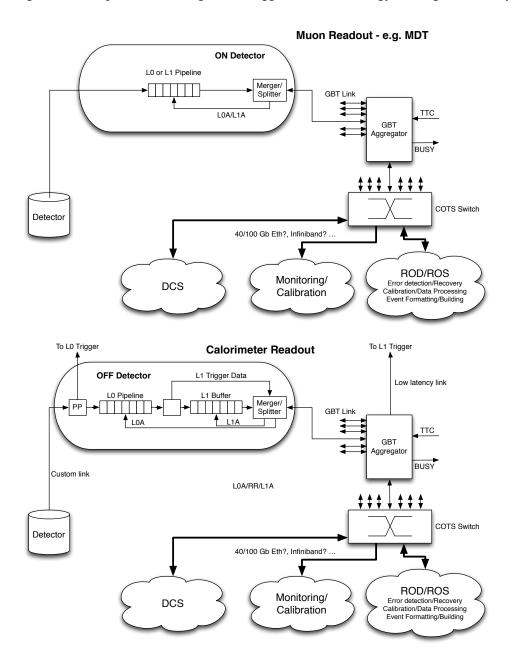

A block diagram of the architecture is shown in Figure 2.2. A more detailed description of the Phase-II trigger and DAQ system is given in the following sections.

**Figure 2.2:** A block diagram of the architecture of the split Level-0/Level-1 hardware trigger proposed for the Phase-II upgrade. (The MDT trigger is shown as part of the Level-1 but may be used at Level-0).

#### 2.1 Projected trigger rates for the Phase-I trigger at HL-LHC luminosities

The Phase-I Level-1 trigger [2] is composed of the Level-1 calorimeter trigger (L1Calo) and the Level-1 muon trigger (L1Muon). The resulting triggers and regions of interest are combined in the Topological Processor and Central trigger system where the Level-1 accept is generated within a latency of 2.5  $\mu$ s. The trigger rate is limited to  $\lesssim 100\,\text{kHz}$  by the detector readout capability.

The performance of the Phase-I system at Phase-II luminosities is taken from a simulation of the functionality of the new electron feature extractor (eFEX) and extrapolations of the performance of the muon trigger based on current data. The performance of the Phase-I trigger at Phase-II luminosities is summarised below.

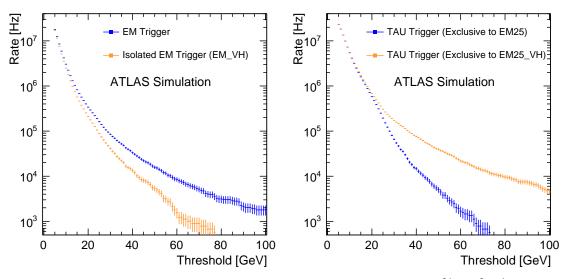

The rates for isolated electrons/photons and for isolated taus have been obtained from a simulation of the Phase-I L1Calo trigger with  $\langle \mu \rangle = 115$ , corresponding to a luminosity of  $\sim$  $4 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. For Phase-II luminosities, the increased granularity still gives improved discrimination for electrons and taus. The expected rates, plotted as a function of trigger threshold are shown in Figure 2.3. In the case of the tau triggers, two curves are shown, the inclusive tau trigger rate and the exclusive rate which does not include electron triggers. For these plots, it has been assumed that new Phase-I L1Calo-based triggers maintain a 95 % efficiency for electrons. For the tau leptons, the efficiency is assumed to be 95 % relative to the current Level-2 selections. The projected trigger rates for an electron trigger threshold of 25 GeV is 250 kHz without hadronic isolation and 125 kHz with hadronic isolation (EM VH). In order to reduce the electromagnetic trigger rate to approximately 20 kHz, a threshold of 40 GeV would be required. This would have a significant impact on ATLAS physics at the HL-LHC and provides strong motivation for the upgrade of the trigger. The situation with tau triggers is less clear. For a tau trigger threshold at 40 GeV, most of the trigger objects are picked up by the EM trigger with a threshold of 25 GeV, but only if hadronic isolation is not used. If only EM triggers with hadronic isolation are assumed, the exclusive tau trigger rate for a 50 GeV trigger threshold is approximately 50 kHz. Either way, the combined EM\_25 and TAU\_40 trigger rate is around 250 kHz.

**Figure 2.3:** The projected trigger rates for  $<\mu>=115$  corresponding to  $\sim 4\times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> as a function of trigger threshold for isolated electron and tau triggers based on a simulation of the electron eFEX. For the tau triggers, the exclusive rates for triggers which do not generate an EM trigger at the corresponding electron threshold are also shown with respect to the EM trigger at half the tau threshold, with and without hadronic isolation.

The Phase-I upgrade of the Level-1 muon trigger consists of replacing the the muon endcap inner trigger station by the New Small Wheel detectors covering the pseudorapidity range  $1.2 < \eta < 2.4$ . The New Small Wheel improves the tracking and results in a sharper  $p_T$  threshold that significantly rejects backgrounds from muons with low  $p_T$ . The performance of the Phase-I muon trigger at Phase-II luminosities has been estimated based on existing data supported by Monte

Carlo studies. The estimated rate for a trigger threshold of 20 GeV is at least 40 kHz, depending on the assumptions for the background rates.

# 2.2 The Phase-II Trigger Architecture

The requirements of the Phase-II hardware trigger are driven by the ATLAS physics goals at the HL-LHC and the constraints imposed by the readout of the detector subsystems. From the perspective of physics, the trigger must maintain thresholds for electrons and muons at between  $20-25\,\text{GeV}$ , and should maintain sufficient flexibility to adapt to emerging physics scenarios. The constraints from the detectors are, in some ways, more difficult to define as they are closely tied to the possibility of replacing/upgrading the readout electronics and data buffering capacity. With this caveat, Table 2.1 summarises the anticipated constraints on the trigger system from the readout of the detector subsystems in terms of both rate and latency. The most stringent requirements come from the MDT. Here approximately 30% of the electronics of the Barrel Inner (BI) Layer of the muon spectrometer is very difficult to access. The implications for the Level-1 trigger latency of the muon readout are discussed in section 5. The constraints imposed by the MDT detector system are met by a Level-1 accept that satisfies:

Rate

$$\leq 200 \,\mathrm{kHz}$$

and latency  $\leq 20 \,\mu\mathrm{s}$

A number of possible Phase-II trigger architectures have been considered. One possibility would be a single stage trigger, along the lines of the current system, formed from the existing calorimeter and muon triggers with a Level-1 trigger accept (L1A) at a rate of less than 200 kHz. However, such a trigger is not compatible with the estimated rates at Phase-II luminosities. For example, Table 2.2 shows the current estimates of the Level-1 trigger rates at  $7 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>, based in part on the studies described in the previous section. The trigger rate for single electrons, muons and taus alone exceeds the 200 kHz constraint imposed by the MDT. In addition to the single lepton triggers, which are necessary for triggering on decays such as  $t \to bW \to b\ell\nu_{\ell}$ , it is also necessary to maintain high efficiency for decays to di-lepton and di-photon final states,  $e.g. H \to \tau\tau$  or  $H \to \gamma\gamma$ , and di-object trigger thresholds have to be kept as low as possible. For thresholds in the range 10-20 GeV, the di-lepton/di-photon trigger rate is expected to be of the order of 100 kHz. Even if only 100 kHz is allowed for jet and MET triggers, building in some flexibility and safety factors suggests that a trigger rate of *at least* 500 kHz for the first stage of the ATLAS trigger should be assumed. With the current trigger architecture, the only way of meeting

| Detector | Max. Rate              | Max. Latency          |

|----------|------------------------|-----------------------|

| MDT      | $\sim 200\mathrm{kHz}$ | $\sim$ 20 $\mu$ s     |

| LAr      | any                    | any                   |

| TileCal  | $> 300 \mathrm{kHz}$   | any                   |

| ITK      | $> 200\mathrm{kHz}$    | $< 500 \mu\mathrm{s}$ |

**Table 2.1:** The anticipated constraints on the L1 accept rate and the total latency from the proposed Phase-II readout of the Muon Drift Tube chambers (MDT), the liquid-Argon calorimeter (LAr), the hadron tile calorimeter (TileCal) and the inner tracking system (ITK).

| Trigger    | Estimated L1 Rate      |

|------------|------------------------|

| EM_20 GeV  | 200 kHz                |

| $MU_20GeV$ | $> 40\mathrm{kHz}$     |

| TAU_50 GeV | 50 kHz                 |

| di-lepton  | $100\mathrm{kHz}$      |

| JET + MET  | $\sim 100\mathrm{kHz}$ |

| Total      | 500 kHz                |

**Table 2.2:** The current estimates of the expected Level-1 trigger rates at  $7 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>, based on the Phase-I hardware trigger system. The tau rate is the exclusive rate. The rates for the JET and MET triggers are estimates based on an extrapolation of the current fraction of the trigger budget used for these triggers.

the 200 kHz limit, imposed by the detector readout, would be to raise thresholds significantly above the electroweak scale. The alternative is to bring additional information into the trigger system.

The baseline for the ATLAS Phase-II hardware trigger is to use tracking information to reduce the electron, muon and tau trigger rates to an acceptable level, such that a L1A could be issued at a rate of 200 kHz. The baseline option for implementing a track trigger is a two stage trigger where a Level-0 accept is issued within 6  $\mu$ s at a rate of 500 kHz. On the Level-0 accept, additional information, e.g. track and full granularity calorimeter information, is brought into the trigger system where it is processed with significantly longer latency generating the L1A within a total latency of 20  $\mu$ s at a rate of 200 kHz, thus meeting the constraints imposed by the readout of the detector.

The proposed Phase-II trigger architecture is shown in Figure 2.2. The Level-0 trigger is almost identical to the Phase-I system, although now the L1Calo trigger is based on the digital signals provided by both the LAr and TileCal calorimeter systems, and no longer uses the previous analogue signals. The Level-0 accept triggers the full readout of the calorimeter into a new L1Calo system based on regions of interest (RoIs). Similarly, regions of the inner tracking detector are readout into the L1Track trigger. The Level-0 accept also initiates the new L1Muon Trigger using data from the MDT. The split Level-0/Level-1 trigger provides two options for the detector readout: either the data from the full latency of  $20\,\mu s$  could be buffered and readout on the L1A; or two pipelines could be used, where the full detector data are buffered for the latency of the Level-0 trigger (6  $\mu s$ ) and on a L0A the data are passed into a second pipeline. The estimated trigger rates with the baseline Phase-II architecture are listed in Table 2.3. With the split Level-0/Level-1 hardware trigger the lepton thresholds can be maintained at an acceptable level within the 200 kHz budget.

The Phase-II Level-0 hardware trigger is essentially the same as the Phase-I system. The Level-1 trigger system consists of four new elements

- Level-1 Track Trigger: the Level-1 Track Trigger will provide track parameters for tracks found within the RoIs found at Level-0.

- Level-1 Calorimeter Trigger: The L1Calo trigger would have access to the full calorimeter granularity through the readout from the calorimeter pre-processor modules on a Level-0 ac-

| Object(s)      | Trigger   | Estimated Rate         |                        |  |

|----------------|-----------|------------------------|------------------------|--|

|                |           | no L1Track             | with L1Track           |  |

| e              | EM20      | 200 kHz                | 40 kHz                 |  |

| γ              | EM40      | $20\mathrm{kHz}$       | $10\mathrm{kHz}^*$     |  |

| μ              | MU20      | $> 40\mathrm{kHz}$     | 10 kHz                 |  |

| τ              | TAU50     | 50 kHz                 | 20 kHz                 |  |

| ee             | 2EM10     | 40 kHz                 | < 1 kHz                |  |

| $\gamma\gamma$ | 2EM10     | as above               | $\sim$ 5 kHz*          |  |

| $e\mu$         | EM10_MU6  | 30 kHz                 | $< 1  \mathrm{kHz}$    |  |

| μμ             | 2MU10     | 4 kHz                  | < 1  kHz               |  |

| au	au          | 2TAU15I   | $40\mathrm{kHz}$       | 2 kHz                  |  |

| Other          | JET + MET | $\sim 100\mathrm{kHz}$ | $\sim 100\mathrm{kHz}$ |  |

| Total          |           | $\sim 500\mathrm{kHz}$ | $\sim 200\mathrm{kHz}$ |  |

**Table 2.3:** The expected Level-1 trigger rates at  $7 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> for the baseline split L0/L1 Phase-II trigger. The EM triggers all assume the hadronic energy veto (VH) is used. \*For the photon and di-photon triggers it is assumed that the full granularity in the Level-1 calorimeter trigger will bring an additional factor 3 in background rejection power. The  $\tau\tau$  trigger rate assumes a factor 2 reduction in the tau fake rate from the eFeX. The *exclusive* rates for  $e\tau$  and  $\mu\tau$  are not included as these will depend strongly on the exact trigger menu and trigger thresholds used.

cept. It might be sufficient to transfer the data only from a region around the RoIs identified by the Phase-I calorimeter trigger. The additional processing time available within the total latency of  $20\,\mu s$  would allow further refinement of the EM, tau, jet and energy sum triggers. For example the positions of the electrons would be determined more precisely which would improve the matching with track segments. Furthermore, the fine-grained calorimeter information would improve the quality of the standalone EM triggers, which will be essential in order to maintain reasonable thresholds for photons.

- Level-1 Muon Trigger: A L1Muon system will introduce the monitored-drift-tubes (MDTs) of the ATLAS muon spectrometer in the Muon trigger, at Level-0 or Level-1. This enables track momentum reconstruction to be performed for muons in the MDT acceptance, providing further background rejection against relatively low momentum muons.

- Level-1 Central Trigger: The new Level-1 central trigger would form the final Level-1 accept based on the results of the L1Calo, L1Muon and L1Track trigger RoIs.

#### 2.3 Calorimeter Trigger

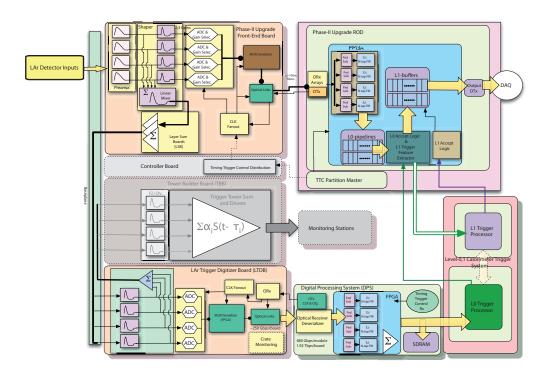

In the Phase-II upgrade, the entire calorimeter front-end and back-end electronics will be replaced, as described in sections 3.1 and 4.1. The new front-end electronics will digitise all channels every bunch crossing and transmit the data off the detector on high speed links to new calorimeter backend electronics in USA15. The fibres would be laid in a low-latency route using the holes in the shielding freed by removing the previous analogue trigger cables. The back-end electronics will process these data every bunch crossing to extract the  $E_T$  and timing of each pulse.

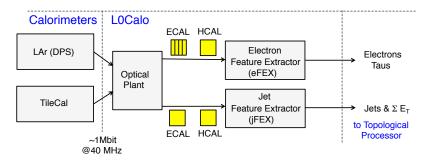

Figure 2.4 shows a functional block diagram for the Phase-II Level-0 calorimeter trigger. The digital signals from the calorimeters are duplicated optically and organised into overlapping detector regions for processing by the electron and jet feature extractors (FEX s). In both cases, the HCAL data are divided into regions of  $0.1 \times 0.1$  in  $\eta$ ,  $\phi$ . The data from the four layers of the LAr ECAL (pre-sampler and three sampling layers of the ECAL) are delivered on optical links in the 1-4-4-1 arrangement, where the first two layers of the ECAL proper are segmented into  $0.025 \times 0.1$  in  $\eta \times \phi$ . For input into the jFEX, these signals are summed in the DPS into a single  $0.1 \times 0.1$  trigger tower. The total number of 10 Gb/s links into the L0Calo would be 4064, comprising 3200 fibres carrying the fine granularity EM layers and 432 fibres carrying the lower granularity data from both the EM and hadronic layers.

Figure 2.4: Functional block diagram for Phase-II Level-0 calorimeter trigger.

#### 2.3.1 Level-0 Calorimeter Feature Extractor

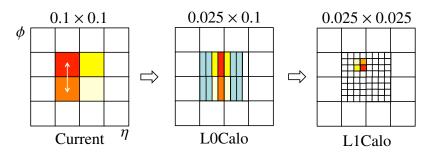

The LOCalo trigger processing will continue to use the Feature Extractor components developed for Phase-I [2], but with modified firmware. The additional information provides further background rejection. An example that has been shown to give a 3-4 times reduction in the trigger rate is to calculate the ratio of the energy in the second layer of the LAr ECAL which occurs in  $3 \times 2$  region of  $\eta - \phi$  centred on the local maximum of  $E_T$  to that deposited in the corresponding  $7 \times 2$  region of  $\eta - \phi$  as illustrated in Figure 2.5, centre.

Figure 2.5: The EM granularity available in the current, Phase-II Level-0 and Phase-II Level-1 EM triggers.

# 2.3.2 Level-1 Calorimeter Trigger

The Level-1 calorimeter trigger will be asynchronous, processing Level-0 accepts as they arrive at an average rate of up to 500 kHz and a peak rate possibly up to 20 MHz. The calorimeter data for

every cell is stored in FIFOs on the calorimeter pre-processor module. On receipt of the L0A for each RoI identified by the Level-0 trigger, the pre-processor modules will send the data for that interaction to the L1Calo system. Each pre-processor module handles a maximum of 2000 cells and will transmit roughly 20 bits per cell, which with an L0Accept rate of 500 kHz, corresponds to a required *average* bandwidth of about 20 Gbit/s per module. (The average bandwidth into the entire L1Calo system would be roughly 2 Tbit/s arriving on up to one thousand 10 Gbit/s links.

The L1Calo system will have access to the full granularity calorimeter data and can therefore deliver improved measurements of the energies and position of the trigger objects. This will result in sharper turn-on curves and more precise matching of clusters to tracks found by the L1Track trigger. The increased granularity available will also provide further background rejection for EM electron and photon triggers. The L1Calo system could also determine more accurate estimates of the  $E_T$  of each object and could apply more sophisticated jet-finding algorithms, which are closer to those performed offline, although the possible performance gains have yet to be studied.

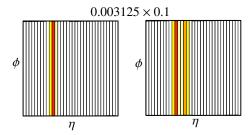

Two additional methods can be used to refine the identification of electrons and photons. The granularity of the data in the second sampling layer of the EM calorimeter is  $0.025 \times 0.025$  in  $\eta - \phi$ , compared to  $0.025 \times 0.1$  in the L0Calo system, as indicated in Figure 2.5 right. Secondly, the significant contribution to the fake EM trigger rate due to photons from  $\pi^0 \to \gamma \gamma$  decays can be suppressed using the  $0.003125 \times 0.1$  segmentation of the LAr strip layer, which provides the first sampling in the calorimeter. As shown in Figure 2.6, a single electron/photon will be concentrated in a single region of the strip layer, whereas the photons from  $\pi^0$  decay may be resolved as two clusters. This provides additional background rejection compared to the layer two information. Furthermore, the strip layer will provide a very fine resolution determination of the  $\eta$  coordinate of any EM RoI. The impact of using the increased granularity on the standalone EM trigger rates is currently being assessed.

**Figure 2.6:** The fine granularity information from the front sampling layer of the EM calorimeter, available in the Phase-I L1Calo trigger, for a photon on the left and  $\pi^0$  on the right.

The results from L1Calo would be similar to those from L0Calo, and would consist of a set of EM, Tau and Jet objects with their  $E_T$  and fine position, together with a variety of energy sums. These would be sent to the Level-1 Central Trigger, which also implements triggers based on event topology, on a single fibre per L1Calo module. Assuming the 500 kHz L0A event rate is handled by ten L1Calo modules in a single ATCA crate, the readout bandwidth is modest, and would not be more than 50 Mbit/s per module assuming that the RoI information is less than 1 kbit.

#### 2.4 Muon Trigger

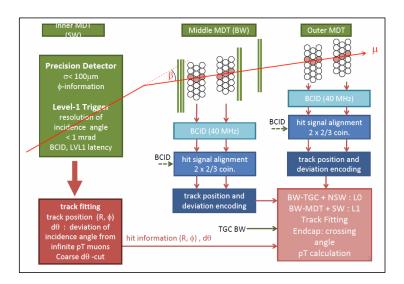

For the required acceptance for physics signatures with muons at the HL-LHC, the  $p_T$  threshold

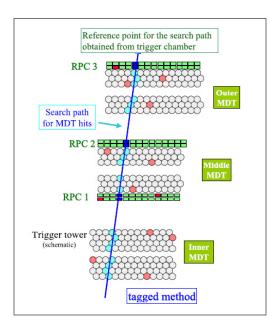

of the Level-1 muon trigger must be no higher than about 20 GeV. To achieve this goal within the split Level-0/Level-1 trigger scheme for the ATLAS Phase II upgrade, upgrades of the current Level-1 muon trigger systems in both barrel and endcap regions are required. Furthermore, to improve the momentum resolution of the muon trigger RoIs and to improve the rejection of poorly measured low-momentum muons, hit information from Monitored-Drift-Tubes (MDTs) is used in the Level-0 or Level-1 trigger decision for the first time. Some aspects of the upgrade of the Level-1 muon trigger are introduced below; a more complete discussion is given in Section 5.

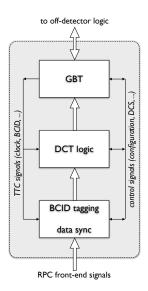

The barrel muon trigger system for the Phase II ATLAS upgrade will make use of the current RPC trigger detectors. However, the electronics will need to be replaced in order to adapt to the new Level-0/Level-1 trigger scheme and to cope with the increased rates and increased latency, which exceed the limits of the current trigger electronics. The majority of the Level-0 trigger logic will be performed in off-detector boards. The on-detector trigger electronics will be primarily concerned with the digitisation of the RPC front-end signals and implementing FPGA-based zero-suppression algorithms, in order to reduce the data bandwidth to the off-detector boards. The replacement of the readout electronics will give the opportunity to improve the tracking performance of the present RPC chambers using time-over-threshold information as a measure of the charge deposited on the strip. The centroid of the charge distribution inside a cluster of adjacent strips will yield an improved measurement of the track position, see section 5.2.1.

After the Phase I upgrade, the muon endcap trigger will be based on hits in the TGC bigwheel (BW) and vector information from new small-wheel (NSW) that provides track-segment information with an angular resolution of 1 mrad and spatial resolution of a few millimetres. The angular information means that track segments which are not consistent with originating from the beam interaction point (IP) can be rejected. The matching in space between TGC-BW RoI and the position of NSW track-segment can also be used to provide further background rejection. Thus, the combination of the BW and the NSW removes most of the RoIs originating from charged-particle tracks which do not come from the IP. This Phase I system forms the basis for the Level-0 muon endcap trigger in the Phase II upgrade. In order to adapt to a new ATLAS trigger scheme, all electronics boards will be replaced with the exception of the Amp-Shaper-Discriminator (ASD) boards and associated cables that are mounted on the chambers. The implementation is described in Section 5.

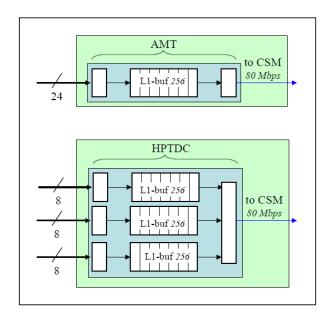

#### 2.4.1 Level-0/Level-1 MDT Trigger

The Level-1 muon trigger rate can be reduced by sharpening up the momentum resolution of muon trigger RoIs, such that the background from lower momentum tracks can be suppressed. In the Phase II upgrade, the monitored-drift-tubes (MDTs) will be used in the Level-0/Level-1 trigger for the first time. The tightening of the threshold curve results in a reduction of the muon rate by a factor of three over much of the detector.

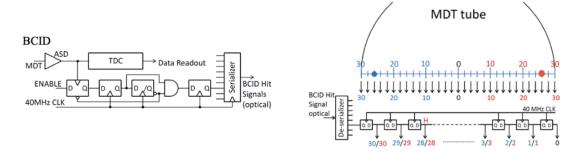

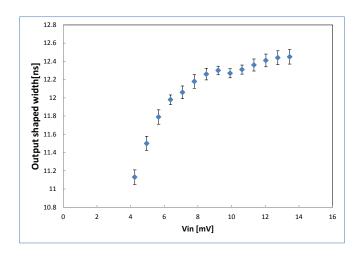

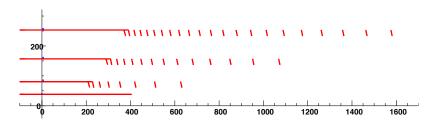

In the front-end boards, the new MDT trigger will implement BCID on a dedicated circuit, shown in the left plot of Figure 2.7, where the leading edges of the hit signals from the ASD's are detected. The BCID hit signals will then be serialised and transmitted to USA15 using high-speed optical links, where they are subsequently deserialized and fed to decoding circuits, as shown on the right of Figure 2.7.

Figure 2.7: The level-0 muon BCID circuits and 31-stage shift register for the Phase II MDT trigger.

The 25 ns bunch-spacing corresponds to a 0.5 mm drift distance in the MDTs. Hence a hit in the 30 mm diameter drift-tubes corresponds to a series of possible incident positions/BCIDs. In the MDTs, this is encoded using a a 31-stage shift-register, where a single BCID hit signal is converted to 61 possible space-time combinations [30, 29,..., 1, 0, 1,..., 29, 30], with the two same numbers corresponding to the two possible drift directions. In the electronics this is achieved by moving a hit signal from one register to the next, from the ends to the centre of the shift register, at the LHC 40 MHz clock speed. The decoded hit signals from each layer can then be aligned in accordance with the expected incidence angle from an infinite  $p_T$  track. Aligned hit signals from the inner, middle and outer stations can then be fed into the track fitting/finding FPGAs and the transverse momentum of the MDT muons can be estimated with a similar quality to the current level-2 muon stand-alone algorithm (MuFast).

#### 2.4.2 Improvement of the RPC trigger

An alternative way to reduce the Level-1 muon trigger rate, by sharpening up the high- $p_T$  resolution of muon trigger RoIs, would be to substantially increase the present RPC system tracking capability. Indeed, the accuracy of the position measurement in the bending direction of the RPC chambers could be improved by using charge distribution in a cluster of adjacent  $\eta$ -strips. The charge measurement can be achieved by exploiting the property of the present RPC front-end electronics that the duration of the output signals of the Amplifier-Shaper-Discriminator chip is correlated with the input charge. Measuring the duration of the signal with a TDC would thus deliver the charge distribution in a cluster of adjacent strips. The centroid of the charge distribution could be used as an estimator of the particle position. A R&D project has been started to evaluate the potential of this method in detail.

#### 2.5 Level-1 Track Trigger

The proposed upgrades of L1Calo and L1Muon triggers alone are unlikely to be sufficient to meet the ATLAS physics goals at the HL-LHC. In particular, the L1 electron trigger rates would be unsustainable for thresholds of  $\sim 20\,\text{GeV}$  based solely on calorimeter information. Furthermore, the limited resolution of the L1Muon system makes it hard to achieve sizeable rate reductions with modest increase of the  $p_{\text{T}}$  thresholds.

The only other source of information with the potential to enhance the purity of the events selected at Level-1 is the Inner Detector. Tracking information is already an essential ingredient

in the current Level-2 trigger; where matching tracks found in the Inner Detector with objects in the calorimeters or the muon detectors provides much of the required background rejection. A new hardware trigger, the FTK, that is based on a fast track reconstruction system will provide reconstructed tracks to the High-Level Trigger, is planned as part of the Phase-I Upgrade [2]. This will be used as the basis of a Level-1 track trigger that can be implemented as part of the tracker upgrade.

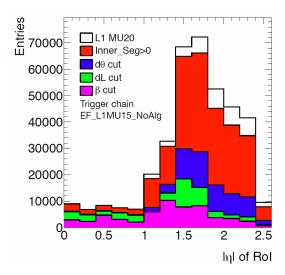

The impact of a track trigger on the Phase-II Level-1 trigger rates has been estimated both using simulation studies and extrapolations of the current Level-1 trigger rates from data. These studies indicate that the inclusion of tracking information in the Phase-II Level-1 trigger can give a factor of five reduction in the rates for L1\_MU20 and L1\_EM18VH single lepton triggers, relative to the rates at Level-0.

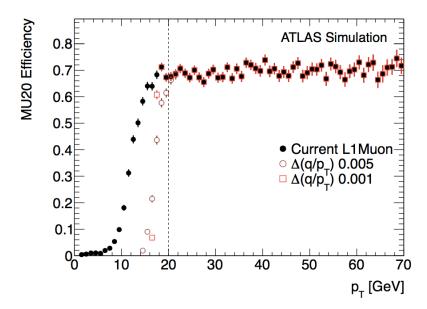

Simulation studies of the breakdown of the muons for  $|\eta| < 1.3$  in terms of their true momentum firing the L1\_MU20 trigger have shown that approximately 80% of the trigger muons have  $p_T < 17\,\text{GeV}$ . This reflects the approximately exponential transverse momentum distribution of muons produced in proton-proton collisions at the LHC and the limited  $p_T$  resolution of the muon L1Muon trigger. Similar performance is expected in the forward region after the installation of the new small wheel in Phase-I. Consequently, if the momentum of the muon RoI can be determined from matching to a L1 track object, then the trigger rate will be reduced by around a factor of five. Figure 2.8 shows the corresponding efficiency curve, showing that using L1Track can sharpen the  $p_T$  turn-on threshold, even with a  $p_T$  resolution that is five times worse than the offline track reconstruction. Fast track reconstruction using a similar approach has been studied up to luminosities of  $3 \times 10^{34}\,\text{cm}^{-2}\,\text{s}^{-1}$  in the context of the ATLAS FTK system [3]. The only additional constraint for the L1Track system is the shorter latency required for processing ( $\sim 6\,\mu\text{s}$ ). This will require a higher level of parallelism in the L1Track system relative to FTK, but this is considered to be achievable.

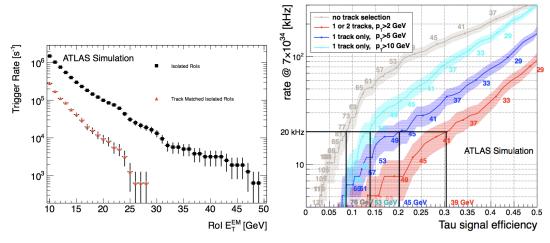

The track trigger can bring similar improvements to EM triggers by providing additional discrimination against the relatively large background rate from electromagnetic energy deposits due to charged pions and photons from  $\pi^0$  decays. For example, Figure 2.9 shows the impact of requiring that the RoIs from the L1\_EM18 Level-0 trigger have a matched track which satisfies  $0.5 < E_T/p_T < 2.0$ ; the trigger rate with track-matched RoIs is ten times smaller than without track-matching. The rate reduction factor is even higher when Level-2 quality EM clusters are used for the track matching, indicating that the benefits from L1Track are complementary to any rate reduction that can be achieved by improving the L1Calo system. Finally, the right plot of Figure 2.9 shows the impact of the track association for RoIs passing the current L1\_TAU trigger. For a constant 20 kHz trigger budget, the inclusion of a track trigger based on requiring 1 or 2 tracks with  $p_T$  greater than 2 GeV will reduce the  $E_T$  threshold required from 76 GeV, corresponding to an efficiency with respect to offline tau candidates with ET>20 GeV of only  $\sim 0.08$ , to 39 GeV providing an efficiency with respect to offline reconstructed taus of  $\sim 0.3$ .

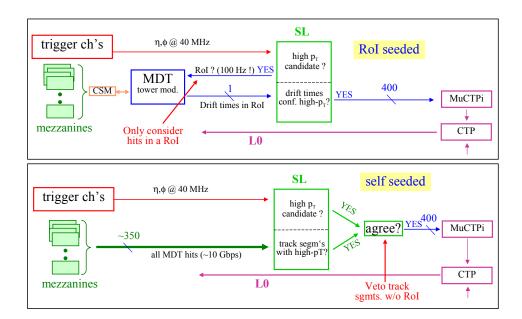

#### 2.5.1 RoI-driven L1Track

The baseline design for the L1 track trigger uses an RoI based approach. The RoI-driven L1Track trigger would provide *all* tracks in a number of relatively small regions of the inner tracking detector, where the regions considered are defined by the EM and muon RoIs from the Level-0 trigger,

**Figure 2.8:** The L1\_MU20 trigger efficiencies as a function of true  $p_T$  after matching with a true muon assuming a track trigger with different  $p_T$  resolutions, assuming that all tracks are reconstructed.

and can only be implemented in a split Level-0/Level-1 trigger architecture. The alternative self-seeded design that aims to reconstruct high- $p_{\rm T}$  tracks in the *entire* tracker is also being investigated. The full data from the Inner Detector cannot be read out at the full beam-crossing rate or even

**Figure 2.9:** Left: the trigger rate vs. L1 EM Cluster  $E_T$  threshold for simulated minimum bias events with  $\langle \mu \rangle = 70$ . Right: rate vs. tau finding efficiency curves for taus from the decay of a 120 GeV Higgs boson for the inclusive tau trigger at  $7 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> for different track multiplicity and minimum track  $p_T$  requirements. The bands show the rate vs efficiency parametrised for different L1 cluster  $E_T$  thresholds, shown as the small numbers next to the corresponding points on each band. The thresholds for each band, such that the integrated rate from the trigger is 20 kHz, are shown at the bottom of the plot. The rates are estimated using simulated minimum bias events at  $3 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> and extrapolated to  $7 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>.

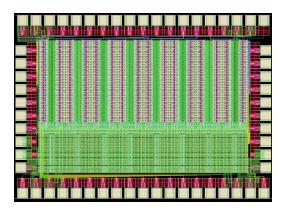

at the Level-0-Accept rate of approximately 500 kHz. The regional readout design of the track trigger addresses this problem by starting from the Level-0 trigger RoIs and then reading only a subset of the tracker data. Conceptually, this is similar to the current design of the ATLAS Level-2 trigger, except that between the Level-0-Accept and the Level-1 decision the data are buffered ondetector in the inner detector readout electronics, as shown in Figure 2.2. After a Level-0 trigger, the data in the front-end chips are copied to a second buffer and labelled with a Level-0 identifier. Some time later, an RoI map device sends a Regional Readout Request (R3) to selected detector front-ends, using information from the Level-0 trigger to identify the modules whose data should be read out. This subset of front-end data is sent to the associated RODs and multiplexed into the main readout data stream. The ROD separates the R3 data from the main readout data and sends them to L1Track. The tracking information from the L1Track trigger would be combined with the output of the L1Calo and L1Muon systems in the central trigger processor. One of the main advantages of the RoI-driven L1Track design is that it has little impact on the inner detector layout which, apart from the depth of the front-end buffers, can be optimised almost independently from the design of the trigger. The double buffering and digital logic for the regional readout has been implemented in the design of the front-end readout ASICs for the strip tracker upgrade and the overall functionality will be tested with prototype chips when they are available in 2013.

The main challenge for the RoI-driven L1Track trigger is to fit within the ATLAS Phase II trigger latency constraints of 20  $\mu$ s. Preliminary results from latency studies using a discrete event simulation show that more than 95% of the regional data can be read out within 6  $\mu$ s, with appropriate prioritisation on the hybrid and assuming 160MHz readout lines, which increases to close to 100% if the speed of the readout lines was increased to 320MHz. This would imply that the latency available for pattern recognition is of similar magnitude, which is considered to be feasible in ten years based on the expected evolution of the hardware that will be used for the FTK project [4].

#### 2.5.2 Self-seeded L1Track

The self-seeded L1Track design performs a fast track reconstruction of *all* high momentum tracks  $(p_T > 10 \text{ GeV})$  in the full coverage of the tracker without requiring external seeds. The huge amount of data makes it impossible to process all hit information from the inner detector for every bunch crossing with currently available technology, so only a subset of selected strip layers would be used for trigger processing. The strategy is to reduce the number of trigger layers to a minimum, while retaining sufficient redundancy in the system and minimising the fake track rate.

For the self-seeded track trigger, a data reduction scheme has to be applied in the detector front-end system in order to remove hits originating from low-momentum tracks at the earliest possible stage. For this, two methods can be exploited: using hits with a small cluster size and inferring the transverse momentum of charged particles from the lateral inclination angle between the hits of stacked double strip layers. In simulations, it is found that these two methods can reduce the bandwidth by about two orders of magnitude for  $p_T > 20 \, \text{GeV} \, [5,6]$ . The exact performance depends on the detailed design of the layout of the inner detector layers. The design requirements for self-seeded track trigger have not been implemented in the current design of the upgraded tracker.

The positions of the hit coincidences in the stacked strip layers are sent to track-finder units which perform a global hit matching in the L1Track processor boards. The expected data rate at

the HL-LHC is about 4 Gbps per stave. This is believed to be sufficiently low that high-momentum tracks can be obtained with a small fake rate. There are a number of open technical questions with the self-seeded L1Track concept, including the implementation of the front-end filtering algorithms, the front-end read out of the trigger information and the technology choice for the fast pattern look-up in the L1Track processor boards.

#### 2.5.3 L1Track pattern recognition and FTK upgrade for Phase-II

The associative memory (AM) technology used in the FTK for the pattern recognition would also be a prime candidate for the L1Track pattern recognition strategy. The very high level of pile-up and the larger number of silicon detector layers, compared to the current ATLAS, would inevitably require a much larger number of patterns to be stored in the AM chips in order to achieve high efficiency for real tracks and low level of fakes. Therefore, the effort to develop new generations of the AM chip, using novel ASIC design technologies (e.g 3-D) is essential for the ATLAS Phase-II programme, regardless of whether such a chip will be used for an upgraded FTK or for the L1Track pattern recognition. Studies will also be required to optimise the pattern recognition hardware, including the data formatting and data preparation, and the potential use of hit filtering, profiting from the few millimetres spacing between the double layers of silicon wafers in the strip detectors, to reject early hits from low momentum tracks.

#### 2.6 Central Trigger System

The main advantage of the proposed L0/L1 architecture is the availability of additional inputs to the trigger decision, which would otherwise not be made available at the bandwidth and latency required for the first trigger stage. The split L0/L1 design is shown in Figure 2.2, which shows the elements of the central trigger system at L0 and L1: the central trigger logic, the Trigger, Timing and Control (TTC). While the block diagram clearly shows the different roles the L0/L1 Central Trigger (CT) play in the system, the physical implementation could well be an integrated design, for example electronic boards housed in the same crate. If possible, the trigger functionality will be carried out using generic boards, which share the same interfaces and design, and which are dedicated by means of specialised firmware to the functionality of the L0 or L1 trigger respectively. The following two sections outline the proposed design of these two stages, while another section is concerned with the Trigger, Timing, and Control (TTC) system, which is used to distribute the Trigger and Timing signals within ATLAS, and between ATLAS and the accelerator. The TTC system is also expected to be redesigned for the needs of the Phase-II upgraded detectors and machine. A block diagram of the split L0/L1 design is shown in Figure 2.2.

As mentioned below the subsystems will have a choice whether or not to participate in L0, hence a whole range of functionalities will be made available for both the L0 and L1 CTP. Among these are the flexible generation of trigger items from the available inputs, pre-scaling of trigger items, bunch group masking, dead time generation and trigger veto handling, as well as the online monitoring of the trigger rates, dead-time, and busy fractions. In addition the trigger on both levels will be partitionable, with one main partition feeding the data acquisition for the physics running, and up to three further partitions for testing and commissioning purposes. that derive their trigger signals from a subset of the trigger menu used for the main partition, but have separate veto and dead time handling.

The L0 Central Trigger (L0CT) combines the functionality of the L0CTP and the Topological Processor. It resembles the Phase-I system in that it receives its main inputs from the L1Calo and L1Muon Trigger processors plus additional trigger inputs, for example from forward and luminosity detectors, and a trigger derived from the signals recorded in the MDT chambers if it is implemented at L0. However, a new system will be required for the Phase-II upgrade to ensure that the Phase-I system does not impose constraints on the Phase-II system. The LOCT has to provide trigger accept signals at rates of at least  $500 \,\mathrm{kHz}$ , while fitting into the overall L0 latency of  $6 \,\mu\mathrm{s}$ . The L0 muon and calorimeter trigger systems will identify regions of interest, that are used in a topological trigger system in order to perform trigger algorithms based on correlations between different types of trigger objects, such as muons and jets. The regions of interest identified at L0 may be used to seed the inner detector and muon trigger at L1. The current candidate electronics standard for the implementation of the LOCT is ATCA, using high-speed optical links for both incoming trigger signals and outgoing trigger and timing signals. A limited number of electrical inputs can be made available for specific use cases and system tests. Trigger signals will be delivered to all sub-systems by the TTC as discussed below, however subsystems can decide if they want to readout on receiving a L0 accept or not.

The L1CT in many ways resembles the L0CT in that it forms a logical combination of both the results of the L0CT and additional detector inputs, namely the L1 Track Trigger, the L1Calo Trigger, and the L1Muon Trigger derived from the signals recorded in the MDT chambers if it is implemented at L1. Again the trigger objects will be made available to a topological trigger processor, which in turn will provide the output of the topological trigger algorithms to the CTP of L1CT. For the L1 trigger the required accept signal frequency is at least 200 kHz, while the overall latency of this trigger stage is  $20 \,\mu s$ . Given the desire to integrate the L0CT and L1CT systems if possible, it is clear that the candidate technologies are the same, namely ATCA with high speed optical links for the signal input and output interfaces. The trigger signals from the L1CT will be distributed to all subsystems. Here all sub-systems need to participate in order to trigger the readout of detector data for the following stages of trigger and data acquisition.

For the Phase-II upgrade it is foreseen to introduce upgraded systems for both the data transfer between the detector front-ends and back-ends, and for the distribution of trigger and timing signals. One of the requirements in introducing these new systems is to maintain backward compatibility with the legacy TTC system, as subsystems will still be using the TTCrx receiver components after the upgrade.

For the communication between the detector front-ends and back-ends a new bidirectional standard is foreseen which will carry trigger and timing signals, control signals, as well as readout data. This link system consists of on-detector and off-detector GBT elements connected by a Versatile Link.

For the upgrade of the off-detector trigger, timing and control system, the basic requirements are bi-directionality and increased bandwidth with respect to the current system, while maintaining backward compatibility. In addition flexible partitioning should be possible, and the new system will accommodate the requirements of different clients (accelerator and experiments) in order to allow the use of a common system. The current optical network implements a point to multipoint architecture with relatively high bandwidth downstream and lower bandwidth upstream. This is the typical topology of a Passive Optical Network (PON), with extra requirements on clock recovery

and fixed latency signals added. The current demonstrator model for the new PON system using 1G-EPON components has a downstream bandwidth of 1.6 Gb/s or ten times the current TTC system for about twice the transmission latency. The upstream bandwidth is 800 Mb/s, where the actual payload and latency depends on the splitting ratio of the system. The current plan is to use 10G components for the final system, which should dramatically improve the values for the demonstrator given above.

# 2.7 Data Acquistion

As described in this document, changes are required to the ATLAS detector to meet the challenges of operating at a peak luminosity of  $7 \times 10^{34}\,\mathrm{cm^{-2}\,s^{-1}}$ . The increased Level-1 accept rate and expected event size (> 4 Mbyte) alone indicate that at least a factor of four increase in bandwidth will be required compared to the data acquisition system that will be in operation up to the Phase-II shutdown. Changes to the detector readout architecture to cope with these requirements are described in Section 2.7.1. Other functions of the data acquisition will also have to evolve to meet the challenges imposed by increased: level-1 accept rate, the rate and quantity of data that will have to be transported from the detector readout to the HLT, event building and throughput to the mass storage. The rate and bandwidth requirements will pose particular challenges to the data acquisition networks and may necessitate a change of architecture and network technology to meet the extended performance requirements. As described in Section 2.8, a  $\langle \mu \rangle$  value of 200 implies a significant increase in the average event processing times, even taking in to account the increase in compute power per node that technology evolution can expect to provide. Subsequently an increase in HLT computing power, and its associated infrastructure, will be required beyond that which will be in operation up to the Phase-II shutdown.

Experience has indicated that evolutions in hardware technologies necessitate equivalent upgrade of software technologies used in a data acquisition so as to fully exploit the full potential of the underlying hardware technology. For these reasons following a period of targeted technical evaluations, particularly in the areas of network technologies, online databases, information sharing and expert systems, new open-software technologies will be selected and where necessary the data acquisition software re-designed and implemented.

The upgrade of the data acquisition system will leverage the changes that will have been implemented for Phase-I operations and where it is necessary to meet the additional Phase-II performance requirements, leverage technology advances expected in the domain of commodity computing and networking. However, given the long lead time to Phase-II it is premature to present details of a possible data acquisition architecture that will be so dependent on technology evolution.

# 2.7.1 Readout System

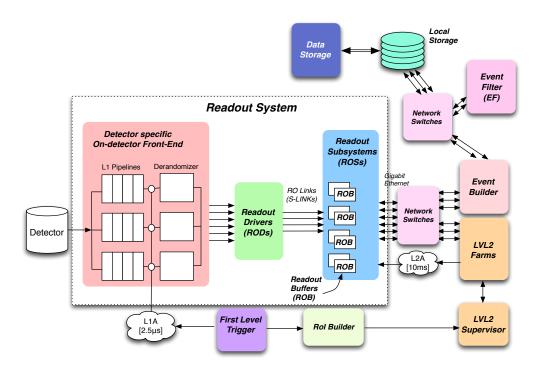

The ATLAS dataflow architecture is schematically depicted in Figure 2.10. The readout system is the "core" of the dataflow and interfaces the detector-specific front-end to the DAQ/HLT units which build and filter the events before the data are transferred to mass storage. In general terms, the following functional blocks can be identified:

• Detector front-end (FE) electronics: conditioning and digitization of the analog input signals, implementation of the Level-1 pipelines and derandomizing buffers, transmission of the FE

data stream on a Level-1 Accept (L1A) trigger.

- Readout Drivers (RODs): multiplexing of several FE data streams, optional processing (e.g. calibration and signal feature extraction), formatting of the FE streams into output ROD fragments.

- Readout Links (ROLs): transmission of the ROD fragments at the L1A event rate. Currently based on the S-LINK protocol, they provide XON/XOFF flow control and error detection.

- Readout Buffers (ROBs): temporary storage of the ROD fragments during the LVL2 decision making and event building, buffer management, error detection and recovery, diagnostics and on-line monitoring.

- Readout Systems (ROSs): housing and control of the hardware modules (ROBIns) that implement the ROBs, buffering and multiplexing of several ROB's into a single event builder input, and servicing Region of Interest (RoI) requests to LVL2.

Figure 2.10: System overview of the ATLAS dataflow and readout system

The flexible design and implementation of today's readout system has enabled the readout system to be consistently operated beyond its design specification, reflecting the evolving needs of ATLAS during the first years of operations. However, the performance of this implementation will become incompatible with the conditions at the HL-LHC because of increased Level-1 trigger rates, new latency specifications, and significantly more challenging data bandwidth requirements: e.g. the maximum ROL bandwidth today is 160 MB/s is based on a ROD fragment size of 1.6 kB for a L1A trigger rate of 100 kHz, while at HL-LHC the event-size will increase significantly because of pileup and an L1A trigger rate of at least to 200 kHz. Furthermore, component ageing will also become

a concern: most of the electronics will be at least 15 years old, raising issues of maintenance and reliability on the timescale of the Phase-II operations.

For the upgrades, total production costs and ease of maintenance during the HL-LHC operation should be one of the prioritized design criteria. The experience accumulated over several years of operations, emerging technologies and the evolution of commercially available components should allow more commonality across the detector ROD systems in terms of functionalities and implementation.

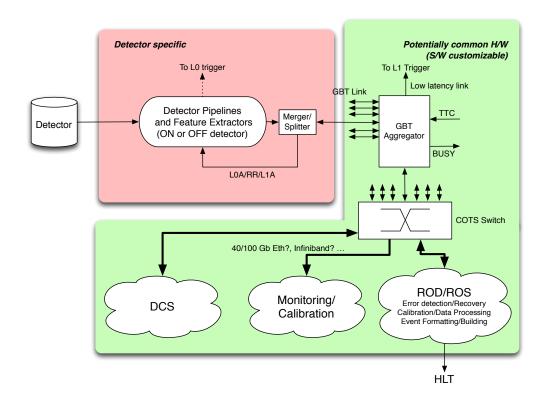

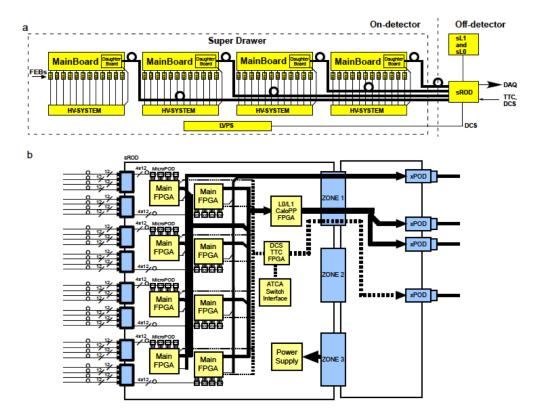

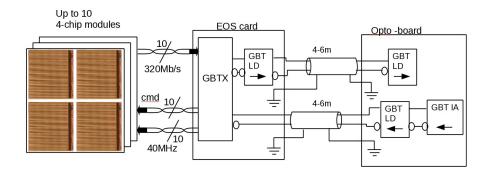

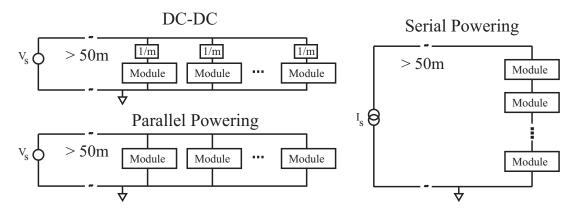

A readout scheme that addresses the need for increased performance, e.g. throughput, at the HL-LHC and places emphasis on commonality is being evaluated by all the ATLAS detector systems, see Fig. 2.11. In this scheme the detector specific FE electronics interface to a common GBT aggregator that implements the multiplexing of FE data streams, data fan-out (e.g. duplication of selected data streams) and translation to standard commercial network protocols. Subsequently the aggregated FE data streams via a commercial high-speed network are routed to the RODs. This allows a common interface for data input to the RODs based on commercial high-speed links.

This scheme, which introduces commercially available high-speed switching networks and links at the earliest stages of the readout and possibly the implementation of a common ROD, introduces several advantages: the capability of re-organizing the readout connectivity without physical re-cabling, scalability and staging capabilities, large scale production of a single ROD design thus lower production and maintenance costs, easier long-term maintainability by avoiding multiple implementations of common functionality (e.g. ROD data formatting), faster and more effective integration and commissioning, and more effective usage of manpower and resources.

Figure 2.11: Readout architecture overview for the Phase-II upgrades

From a technical perspective this scheme also offers the possibility of increased integration between the ROD and ROB/ROS components. The ROD/ROS physical integration would relieve the technical complications of implementing a reliable flow control mechanism (XON/XOFF) across a switched network. It also introduces more flexibility to cope with different trigger strategies, e.g. a more significant component of the high-level trigger selection strategy no longer seeded by RoI.

**Figure 2.12:** Possible implementation of the Phase-II readout architecture for the Muon spectrometer (top) and for the calorimeters (bottom).

Fig. 2.12 illustrates how the readout scheme may be implemented for a Muon detector (MDT)

and the calorimeters. For the former the front-end electronics (on detector) are interfaced directly to the GBT aggregator modules. The calorimeters stream off detector the digitized samples to a Pre-Processor (off detector) that implements the pipelines, processing of the raw data samples and preparing of the L0/L1 trigger primitives. A full analysis of the functional and technical requirements, as well as implementation details detector by detector is ongoing.

# 2.8 High-Level Trigger

The HLT selection software must be upgraded to match the detector upgrades, to maintain HLT rejection following the Level-1 upgrade and to fully exploit the evolution in computer hardware. Following the Phase-II Level-1 upgrade, many of the selection tools that are currently employed at L2 will be moved to L1. This includes tracking, fine granularity calorimeter information and topological triggers. An HLT rejection factor of 20-40 is required to reduce the Level-1 accept rate of 200 kHz to about 5-10 kHz for recording. To do this the HLT will employ offline-type selections which are likely to emphasise multi-object signatures, for example combinations of leptons, jets, jets with b-tagging and  $E_T^{miss}$ . In order to maintain the required HLT rejection, new selection software will be developed to fully exploit the increased computing power available through advances in computer hardware and upgrades to the HLT farm.

Selections will be based on trigger objects reconstructed with near-offline quality. In addition to the refinement of Level-1 objects within the RoIs, whole event reconstruction can be performed by the HLT. Calorimeter clustering will benefit from improved calibration compared to Level-1 and can exploit offline-type tools for suppression of calorimeter noise and pile-up. HLT tracking will be adapted to the new tracker. HLT inner detector and muon tracking will benefit from being able to use the full conditions information and magnetic field-maps, and offline-quality track reconstruction to refine Level-1 information and reconstruct tracks for which there are no Level-1 seeds.

In addition to improvements in cluster and track reconstruction, the software that identifies trigger objects such as leptons and jets will be upgraded. Lepton reconstruction will be upgraded to benefit from offline tools for electron Bremsstrahlung correction, reconstruction of converted photons and secondary vertex reconstruction for hadronic tau decays. HLT code will be upgraded to use more offline-type selections, for example multivariate selections. Event by-event primary vertex reconstruction would allow impact parameter requirements to be applied to suppress pile-up. The HLT jet reconstruction will be upgraded to benefit from advances in offline jet reconstruction algorithms and will be based on full-event information. The addition of track information could be used to reconstruct track-based jets and suppress pile-up by calculating the fraction of transverse energy associated to a given primary vertex.

Significant changes to the HLT software are planned in preparation for Phase II. These changes are needed to exploit the evolution in computing hardware. While it is difficult to predict the precise nature of the changes over the next 10 years, it is likely that the current trend towards increased numbers of cores will continue. The HLT software will need to adapt to fully exploit many-core architectures through the parallelisation of code. This will involve significant changes both to the HLT framework, to support execution of algorithms in parallel threads, and to the algorithms themselves to allow deeper parallelisation e.g. at the level of a track. Substantial effort

will be needed to design and implement these upgrades. Commonality with offline software will be exploited where possible.

# 3. Upgrade of the Liquid-Argon Calorimeter

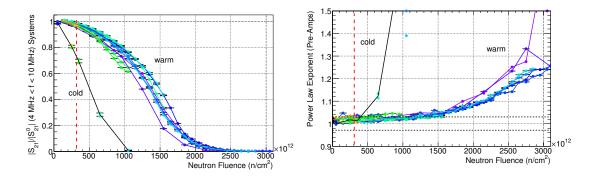

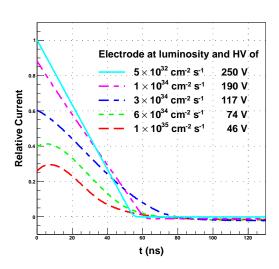

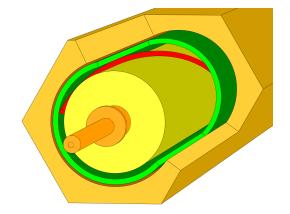

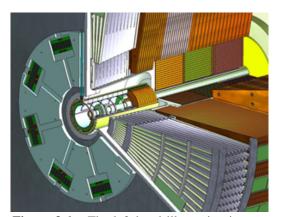

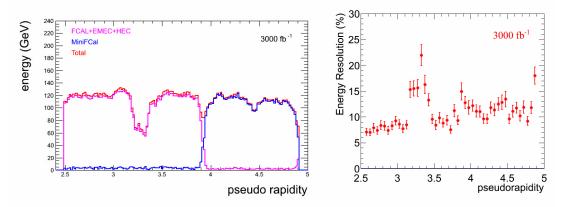

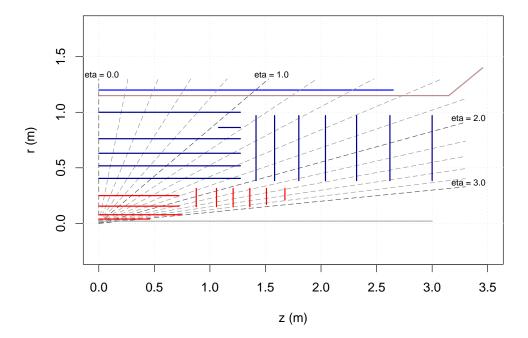

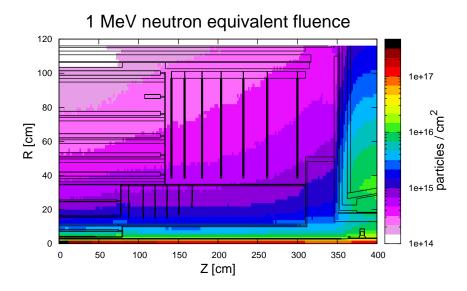

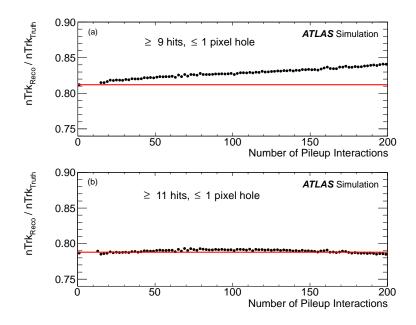

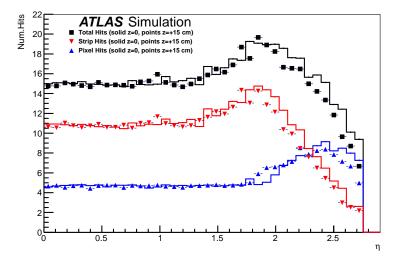

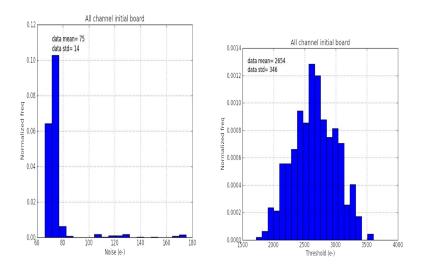

The HL-LHC allows for substantial increases in instantaneous and integrated luminosities at the cost of corresponding increases in radiation damage and operational challenges. During HL-LHC operation, particle fluxes and the average energy deposited in the calorimeters are expected to be typically five to ten times higher than specified in the LHC design values. Furthermore, at the start of HL-LHC operations the current electronics will be 15–20 years old.